At the core of our verification process lies the powerful Universal Verification Methodology (UVM). This industry-standard methodology empowers us to deliver exceptional quality and efficiency in design verification. By harnessing the standardized framework of UVM, we ensure thorough and reliable verification, enabling us to push the boundaries of innovation and achieve unmatched levels of success in complex digital designs.

What is Universal Verification Methodology?

Universal Verification Methodology, or UVM, is a standardized framework used to verify the functionality and accuracy of digital designs such as complex ASICs (Application-Specific Integrated Circuits) and SoCs (Systems on Chip). UVM is built on SystemVerilog; a hardware description and hardware verification language commonly used in the EDA (electronic design automation) industry.

UVM supports engineers to develop modular, reusable and scalabe testbenches, supporting comprehensive pre-silicon validation. This methodology ensures all aspects of the design is tested, reduces the risk of errors and improves the overall design quality.

Why was UVM developed?

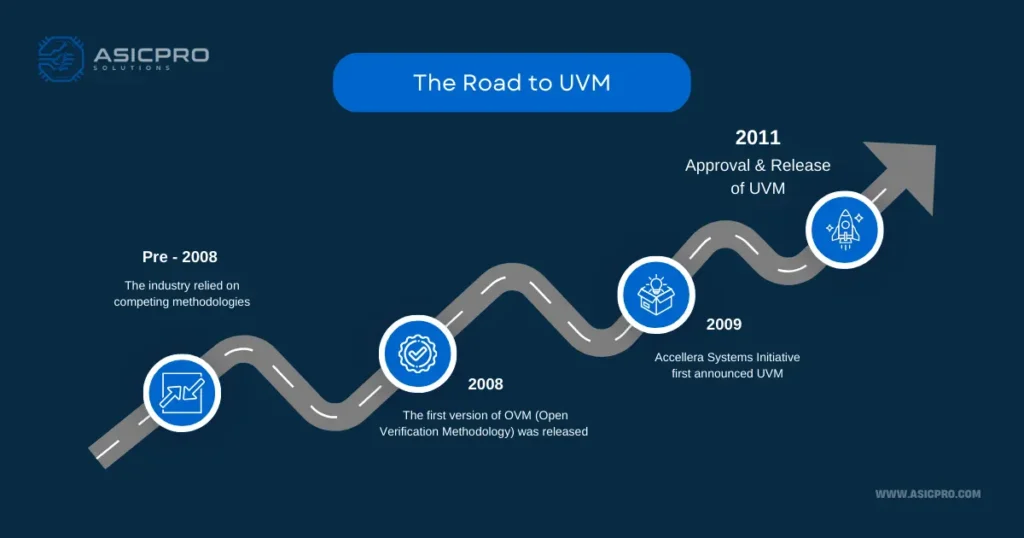

Before UVM, verification engineers relied on different methodologies such as OVM (Open Verification Methodology) and VMM (Verification Methodology Manual). The lack of a unified framework made it difficult to maintain consistent verification practices and often led to fragmentation across the industry. It was clear that an industry-wide solution was needed in order to streamline and standardize design verification best practices.

Key drivers behind UVM’s development included:

- Standardization: Establish a unified verification approach across the semiconductor industry

- Interoperability: Enable reusability of both IP and testbenches across a variety of tools, teams and projects

- Scalability: Support verification of increasingly complex digital designs

- EDA Tool Support: Ensure compatibility with major EDA vendors such as Synopsys, Siemens EDA and Cadence

Now recognised as the gold standard in modern chip verification, UVM has fundamentally changed how engineers work to validate today’s increasingly complex digital designs. The introduction of UVM meant verification teams could begin to build more reliable, reusable and robust test environments – ultimately leading to faster development cycles and more efficient, thorough verification.

Who relies on UVM in the semiconductor industry?

UVM is adopted by leading ASIC and SoC design companies, specialist engineering teams and more. It has become essential for delivering high-quality, scalable verification solutions in applications like AI, automotive and consumer electronics.

Major EDA companies, like Cadence, Synopsys and Siemens, provide support for UVM within their verification platforms. IP providers also leverage UVM to ensure their components are suitable for integration and meet industry standards.

Is Universal Verification Methodology still relevant in 2026?

Certainly! UVM is still the go-to framework and standard for chip verification, driving efficiency, scalability and accuracy in today’s ever-complex designs. By streamlining the verification process, promoting reusability and reducing bugs early on in the design cycle, UVM supports engineers and teams across the industry to meet the growing demands of semiconductor development.

Leveraging UVM for Efficient ASIC Development

At AsicPro, our primary goal is to deliver exceptional services to customers worldwide, addressing the growing demand for efficient ASIC development cycles. We specialize in ASIC Design, ASIC DV/MSDV Verification, 3rd Party IP Integration, Project Planning and more.

Our verification process is underpinned by the Universal Verification Methodology (UVM), which ensures reliability, scalability and accuracy in all aspects of our projects. By leveraging UVM, we streamline complex verification tasks and help our clients to achieve unmatched results.

As trusted partners for ASIC design and verification, our expertise in UVM, combined with our deep technical knowledge, ensures your projects can progress smoothly, from initial concept to final production. With AsicPro, you can trust that your designs will meet the highest standards of quality and efficiency.

Contact Us

Contact our team to explore how our expert design and verification services can bring your ideas to life – efficiently, reliably and with your long-term business goals in mind.